# **Systèmes d'Information Numérique**

S2 : Systèmes séquentiels

R2.07 (1<sup>ère</sup> partie) – BUT I GEII

Michelle VIEIRA (responsable du module)

Contact : [michelle.vieira@univ-grenoble-alpes.fr](mailto:michelle.vieira@univ-grenoble-alpes.fr)

2025-2026

# Planning des séances

| Semestre 2 |        | TD SIN2 (14h)              | TP SIN2 (4h) | CC + DS |

|------------|--------|----------------------------|--------------|---------|

| Sem.       | Séance |                            |              |         |

| 2          | 1      | chap 6 Bascules            |              |         |

| 2          | 2      | chap 6 Bascules            |              |         |

| 3          | 3      | chap 7 Machine à états     |              | CC1     |

| 3          | 4      | chap 7 Machine à états     |              |         |

| 4          | 5      | Chap 8 Compteurs           |              |         |

| 4          | 6      | Chap 8 Compteurs           |              |         |

| 5          | 7      | Chap9 Registres à décalage |              | CC2     |

| 5          |        |                            | TP cablage   |         |

| 6          |        |                            |              | DS SIN2 |

## Acquis d'apprentissage visés au semestre 2

**A l'issue de cette 1<sup>ère</sup> partie de la ressource Automatisme 2**, les étudiants seront capables de :

- (Re)connaître les fonctions de bases de l'électronique numérique séquentielle ;

- Proposer une solution logique ou programmer pour réaliser un comptage, un registre ou une mémoire ;

- Décomposer une fonction en blocs combinatoires et séquentiels

- Choisir et mettre en oeuvre un circuit numérique conventionnel ou programmable

## Evaluation du SIN 2

- **Devoir surveillé de 1h30 en semaine 6, le 05/02/2026**

- Coefficient 1

- Modalité de l'épreuve :

- Seule une feuille A4 recto-verso de notes personnelles est autorisée

- Pas de calculatrice

- En cas d'absence justifiée au DS, en plus de fournir votre justificatif au secrétariat, vous devez **obligatoirement** prévenir Mme Vieira par mail ([michelle.vieira@univ-grenoble-alpes.fr](mailto:michelle.vieira@univ-grenoble-alpes.fr)) **au plus tard 24h après le DS** pour pouvoir être autorisé à participer au rattrapage

- **Moyenne des 2 contrôles continus et du TP**

- coefficient 0,5

- Une absence injustifiée à un CC vous faudra la note de 0 donc pensez à fournir à votre enseignant de TD votre justificatif

## Chapitre 6 : Bascules

### Introduction :

- **système combinatoire** => la sortie ne dépend que de la valeur des entrées

- **système séquentiel** => la sortie peut dépendre de la valeur des entrées et de la valeur de la sortie à l'instant précédent

- bascules = éléments de base des systèmes séquentiels

2

### Plan du chapitre :

- I. Bascule asynchrone RS

- II. Bascules synchrones

- III. Généralités sur les bascules synchrones

- IV. Compléments

3

### I. Bascule asynchrone RS

- bascule asynchrone = bascule dont la sortie évolue dès qu'une entrée change d'état

- bascule RS (ou bistable RS) = seule bascule asynchrone

4

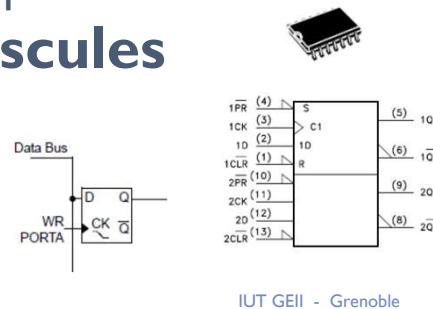

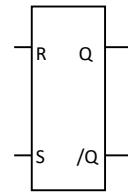

## I. Bascule asynchrone RS : symbole

R : reset (mise à 0)

S : set (mise à 1)

Q : sortie de la bascule

/Q: sortie complémentée

5

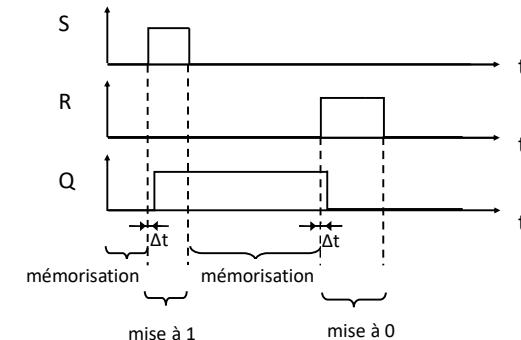

## I. Bascule asynchrone RS : chronogramme

6

## I. Bascule asynchrone RS : table de vérité

| R | S | Q     |                    |

|---|---|-------|--------------------|

| 0 | 0 | $Q_0$ | → mémorisation*    |

| 0 | 1 | 1     | → mise à 1         |

| 1 | 0 | 0     | → mise à 0         |

| 1 | 1 | X     | → état indéterminé |

\*  $Q_0$  correspond à l'état de la sortie à l'instant précédent

7

## I. Bascule asynchrone RS : équation

Tableau de Karnaugh :

|   |   | RS    | 00 | 01 | 11 | 10 |

|---|---|-------|----|----|----|----|

|   |   | $Q_0$ | 0  | 1  | x  | 0  |

| R | S | 0     | 0  | 1  | x  | 0  |

|   |   | 1     | 1  | 1  | x  | 0  |

on pose X = 0 (reset prioritaire)

$$\text{Equation : } Q = /RS + /RQ_0 = /R(S+Q_0)$$

8

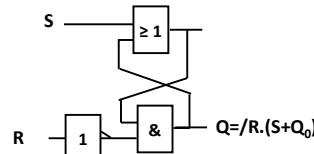

## I. Bascule asynchrone RS : réalisation

avec des NOR

avec des NAND

9

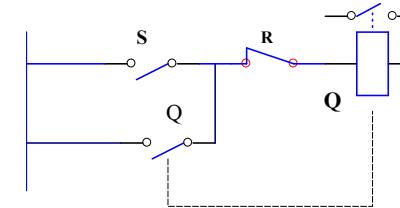

## I. Bascule asynchrone RS : effet mémoire cad auto maintien

Equation :  $Q = \overline{R}(S+Q_0)$

10

## Plan du chapitre :

- I. Bascule asynchrone RS

- II. Bascules synchrones**

- Bascule D

- Bascule T

- Bascule JK

- III. Généralités sur les bascules synchrones

11

## II. Bascule synchrone :

- bascule dont la sortie évolue **uniquement** quand signal d'horloge prend une valeur particulière

- signal d'horloge => **synchronise** l'évolution de la sortie

- changements constatés sur les entrées (autres que l'entrée d'horloge) => pas d'influence immédiate sur la sortie

12

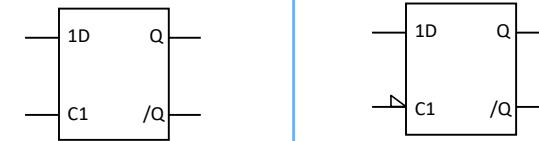

## II. Bascule synchrone D : appelée aussi Flip-Flop

Une bascule D est une bascule synchrone qui possède une entrée D (comme Data) et une entrée d'horloge C qui synchronise soit :

- sur niveau (= LATCH) => peu utilisée

- sur front (= EDGE TRIGGERED)

13

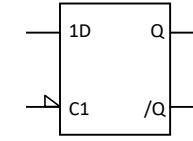

## II. Bascule synchrone D latch : symbole

Bascule D synchronisée sur niveau haut donc

- $C = 1 \rightarrow$  synchronisation active, Q recopie D

- $C = 0 \rightarrow$  synchronisation inactive, mémoire

Bascule D synchronisée sur niveau bas donc

- $C = 0 \rightarrow$  synchronisation active, Q recopie D

- $C = 1 \rightarrow$  synchronisation inactive, mémoire

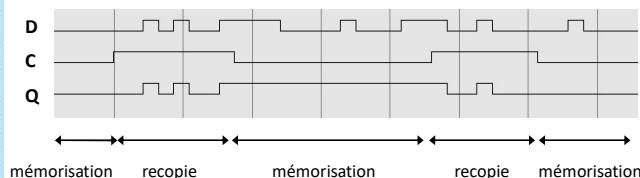

## II. Bascule synchrone D latch : chronogramme

Cas d'une bascule D active sur niveau haut:

15

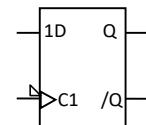

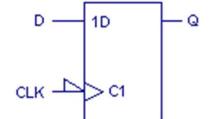

## II. Bascule synchrone D edge triggered : symbole

A chaque front montant de C (Clock CLK), Q recopie l'entrée D

A chaque front descendant de C, Q recopie l'entrée D

16

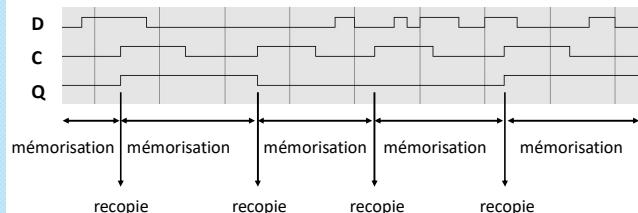

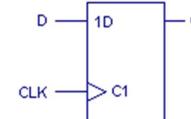

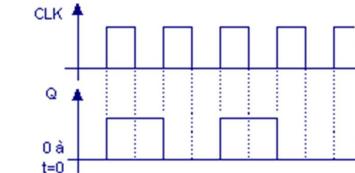

## II. Bascule synchrone D edge triggered : chronogramme

Cas d'une bascule D active sur front montant:

17

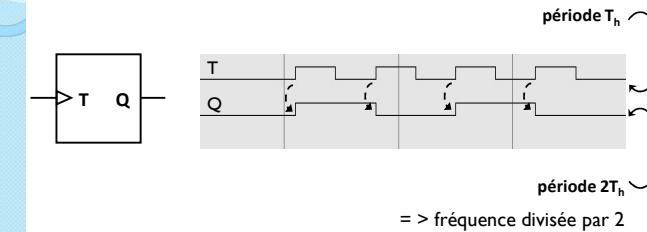

## II. Bascule synchrone T :

=> fréquence divisée par 2

T = toggle = basculement

Changement d'état à chaque front montant de T qui correspond à l'horloge

18

## II. Bascule synchrone T :

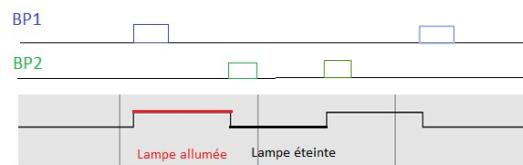

En domotique (ou électricité bâtiment), une bascule T correspond à un télerrupteur où l'horloge est remplacée par un ou plusieurs BP en parallèle

Changement d'état à chaque impulsion d'une des entrées

19

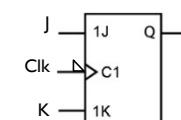

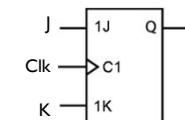

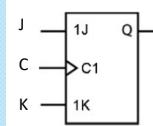

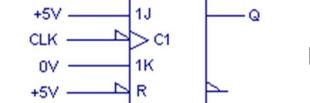

## II. Bascule synchrone JK :

### symbole

JK = RS synchrone sans cas indéterminé

=> J = K = 1 fonctionnement de type T (toggle)

Bascule active sur front montant

Bascule active sur front descendant

20

## II. Bascule synchrone JK : table de vérité

Cas d'une bascule JK active sur front montant :

| Clk | J | K | Q               |                 |

|-----|---|---|-----------------|-----------------|

| ↑   | 0 | 0 | $Q_0$           | → mémorisation* |

| ↑   | 0 | 1 | 0               | → mise à 0      |

| ↑   | 1 | 0 | 1               | → mise à 1      |

| ↑   | 1 | 1 | /Q <sub>0</sub> | → basculement   |

\*  $Q_0$  correspond à l'état de la sortie à l'instant précédent

21

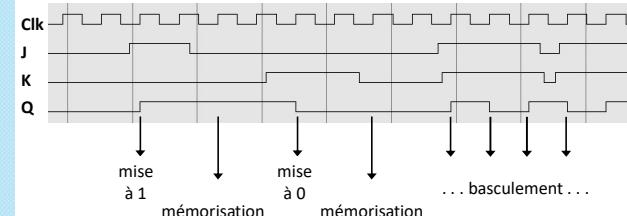

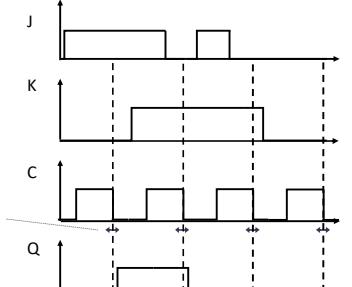

## II. Bascule synchrone JK : chronogramme

22

## Plan du chapitre :

- I. Bascule asynchrone RS

- II. Bascules synchrones

- III. Généralités sur les bascules synchrones

- Entrées

- Caractéristiques dynamiques des signaux d'entrées

- Déclenchement des bascules

23

## III. Bascules synchrones : les entrées

- une entrée d'**horloge** => pour prendre, ou de ne pas prendre, en compte les entrées fonctionnelles synchrones

- + des entrées **fonctionnelles** (pour commander le fonctionnement dynamique du circuit)

- **asynchrones** : agissent indépendamment de l'horloge pour commander le circuit. Elles sont prioritaires par rapport aux entrées synchrones.

- **synchrones** : n'agissent sur la sortie que lorsque le signal d'horloge est actif

24

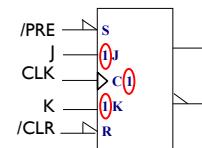

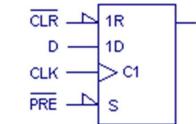

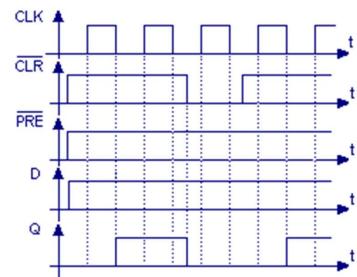

### III.Bascules synchrones : les entrées

Exemple d'une bascule JK active sur front montant avec des entrées fonctionnelles asynchrones:

- Entrées fonctionnelles synchrones : J et K (voir 0)

- Entrées fonctionnelles asynchrones:

- /CLR (ou /clear ou R) pour une mise à 0

- /PRE (ou /preset ou S) pour une mise à 1

- Ici /CLR et /PRE actives à l'état bas

25

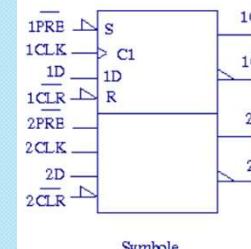

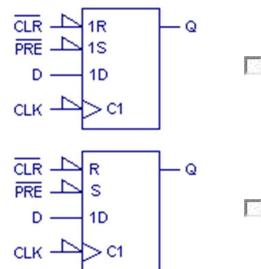

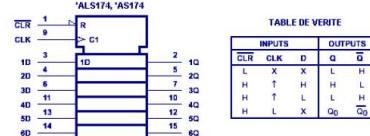

### III.Bascules synchrones : exemple d'entrées

Autre Exemple :

Symbole

Table des niveaux

| INPUTS                  |                         |     |   | OUTPUTS |            |

|-------------------------|-------------------------|-----|---|---------|------------|

| $\overline{\text{PRE}}$ | $\overline{\text{CLR}}$ | CLK | D | Q       | $\bar{Q}$  |

| L                       | H                       | X   | X | H       | L          |

| H                       | L                       | X   | X | L       | H          |

| L                       | L                       | X   | X | H*      | H*         |

| H                       | H                       | ↑   | H | H       | L          |

| H                       | H                       | ↑   | L | L       | H          |

| H                       | H                       | L   | X | Q0      | $\bar{Q}0$ |

\* configuration instable

26

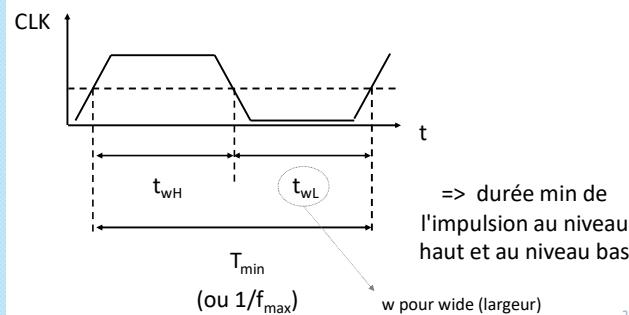

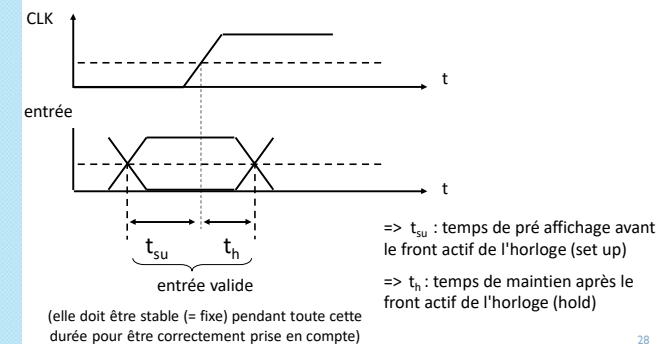

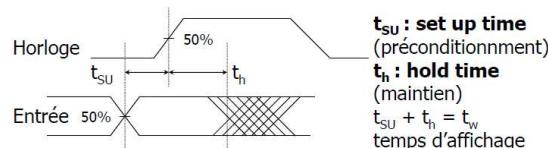

### III.Bascules synchrones : caractéristiques dynamiques

#### fréquence max de fonctionnement

27

### III.Bascules synchrones : caractéristiques dynamiques

#### Stabilité des entrées

28

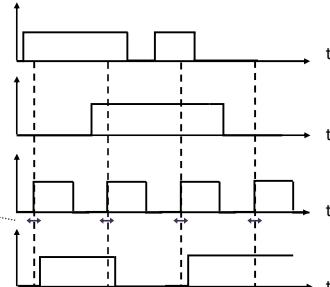

### III. Déclenchement des bascules synchrones

déclenchement par front : EDGE TRIGGERED

exemple

durées pendant lesquelles le niveau sur les entrées fonctionnelles synchrones (ici J et K) doit être stable

29

### III. Déclenchement des bascules synchrones

déclenchement par front : EDGE TRIGGERED

exemple

durées pendant lesquelles le niveau sur les entrées fonctionnelles synchrones (ici J et K) doit être stable

30

### Plan du chapitre :

- I. Bascule asynchrone RS

- II. Bascules synchrones

- III. Généralités sur les bascules synchrones

- IV. Compléments:**

- bascule monostable

- bascule astable

31

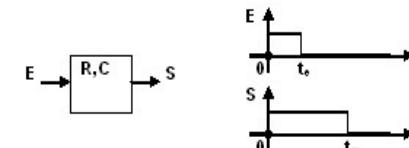

### IV. Compléments : bascule monostable

La sortie de cette bascule ne possède qu'un seul état stable. Sa sortie sera à l'état H (ou L) par déclenchement (front montant sur E par exemple) durant un temps  $t_m$  fixé par une constante de temps (RC)

32

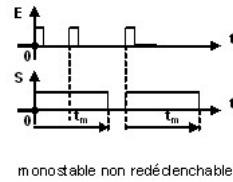

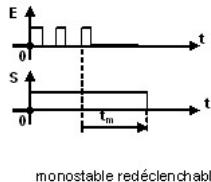

## IV. Compléments : bascule monostable

**MONOSTABLE:** Redéclencheable ou non-redéclencheable ?

To be retriggered or not to be retriggered : that is the question ??

Exemple en électronique numérique : 4538

33

## IV. Compléments : bascule astable

La sortie de cette bascule ne possède aucun état stable. Sa sortie sera à l'état H puis à l'état L pour une durée infinie (ou tant qu'elle est validée). C'est donc une horloge dont la fréquence et le rapport cyclique (durée à l'état H sur la période) peut être réglable.

**Exemple en électronique numérique :** NE 555 (vu en Eln).

**Exemples en automatisme :** fonction clignoteur

34

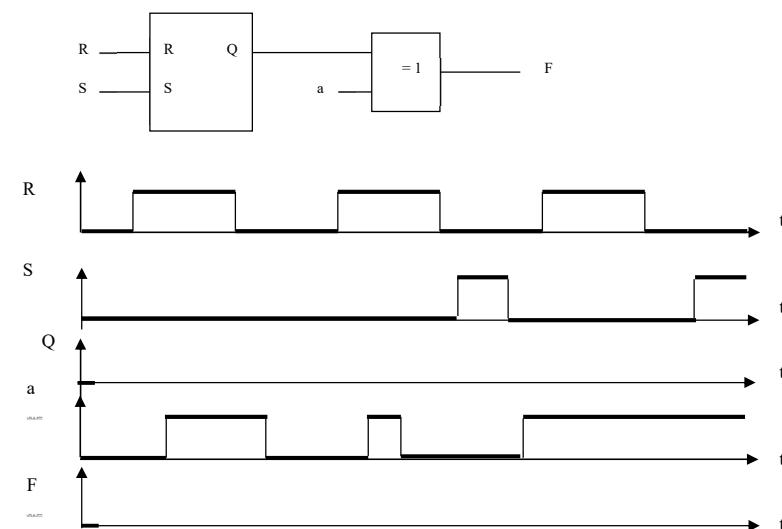

## TD Chap 6 : Bascules

### Exercice 1 :

Complétez le chronogramme représentant le fonctionnement du montage suivant.

On commencera par représenter la sortie Q (initialement à 0) puis en fonction de a on mettra à jour F

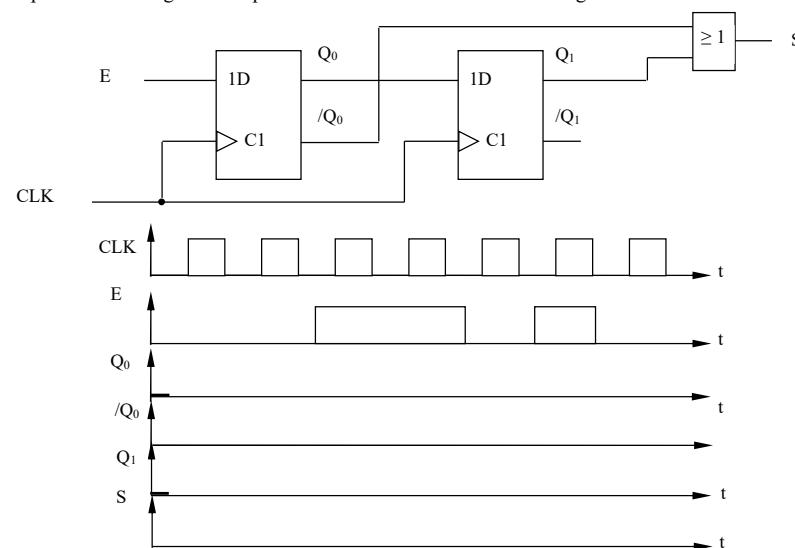

### Exercice 2 :

Complétez le chronogramme représentant le fonctionnement du montage suivant.

### Exercice 3 :

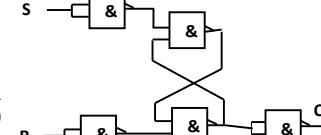

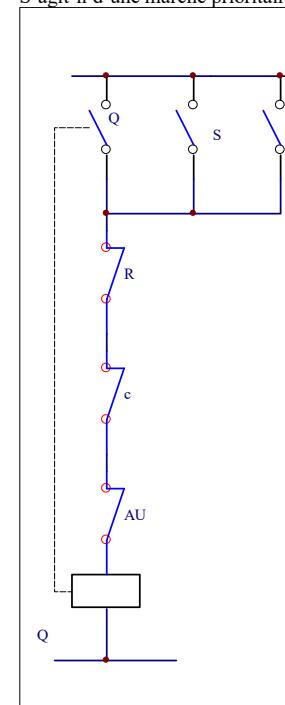

Donner l'équation de la sortie Q d'une bascule bistable avec SET PRIORITAIRE.

En déduire (représenter) le schéma à contact correspondant.

### Exercice 4 :

Donner l'équation logique du schéma suivant.

S'agit-il d'une marche prioritaire ou d'un arrêt prioritaire ? Justifier

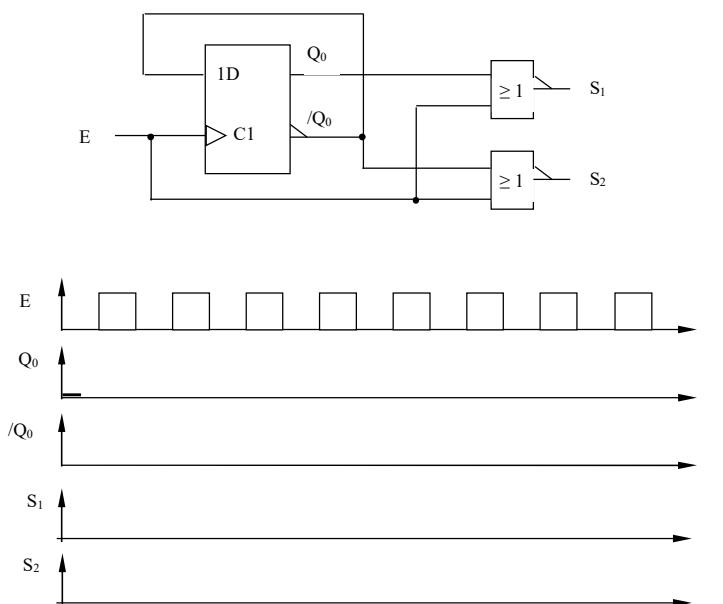

**Exercice 5 :**

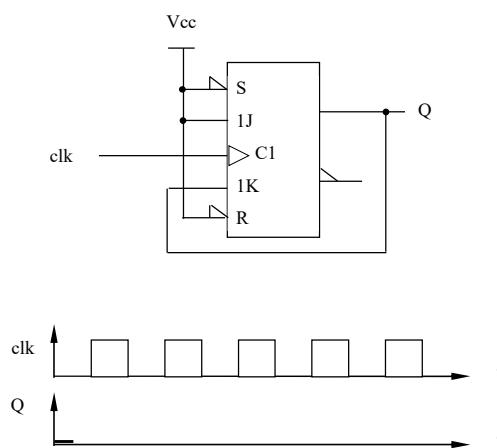

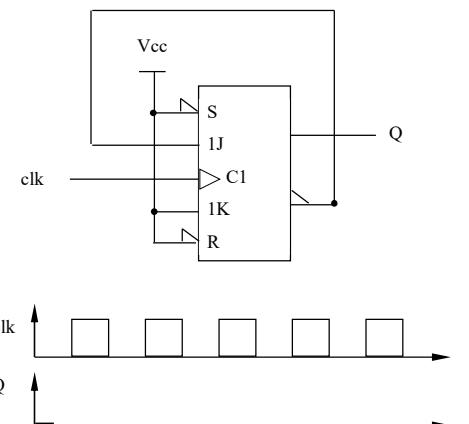

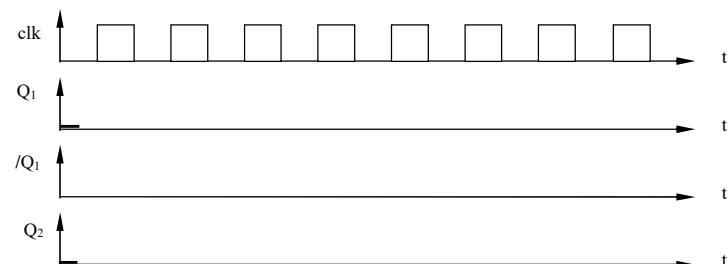

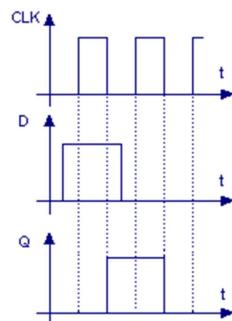

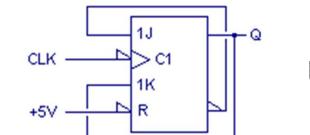

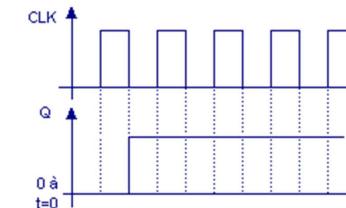

Complétez le chronogramme représentant le fonctionnement du montage suivant.

**Exercice 6 :**

Complétez le chronogramme représentant le fonctionnement du montage suivant.

**Exercice 7 :**

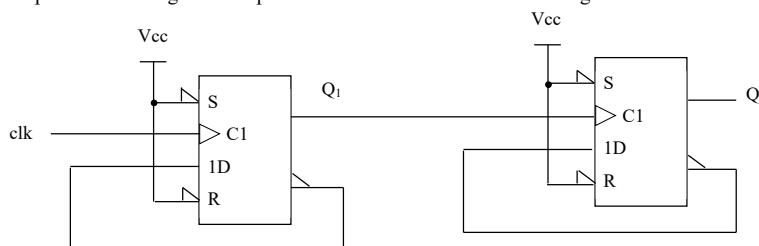

Complétez le chronogramme représentant le fonctionnement du montage suivant.

**Exercice 8 :**

Complétez le chronogramme représentant le fonctionnement du montage suivant.

**Exercice 9 :**

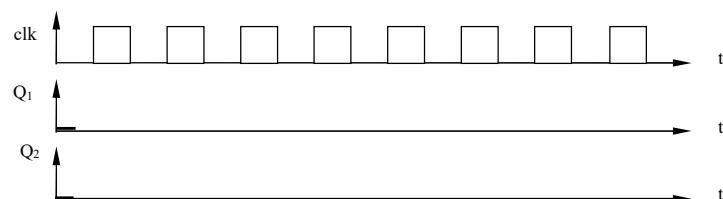

Complétez le chronogramme représentant le fonctionnement du montage suivant.

**Exercice 10 :**

Complétez le chronogramme représentant le fonctionnement du montage suivant.

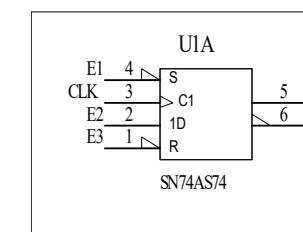

**Test de synthèse :****Question 1**

Indiquer, à quelle type de bascule correspond le schéma suivant :

Bascule D avec entrée de mise à 0 synchrone et entrée de mise à 1 synchrone

Bascule D avec entrée de mise à 0 asynchrone et entrée de mise à 1 asynchrone

Bascule D avec entrée de mise à 0 asynchrone et entrée de mise à 1 synchrone

Bascule D avec entrée de mise à 0 synchrone et entrée de mise à 1 asynchrone

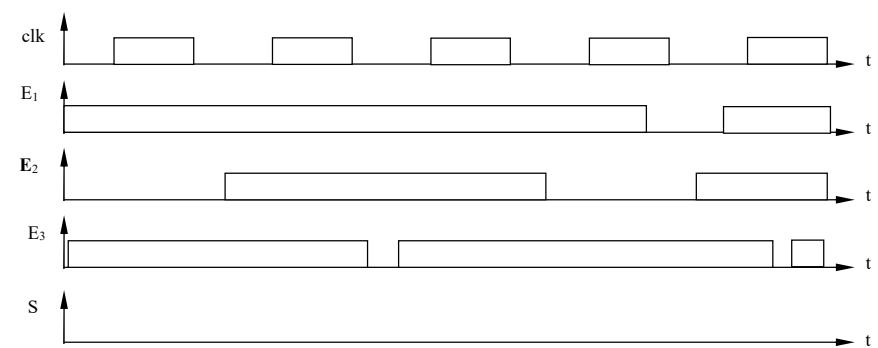

**Question 2**

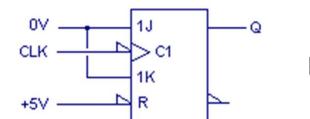

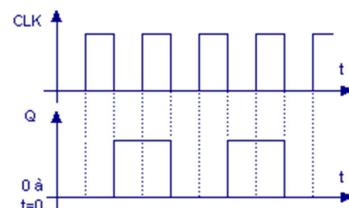

Indiquer à quelle(s) bascule(s) correspond le diagramme des temps suivant :

**Question 3**

Indiquer à quelle(s) bascule(s) correspond le diagramme des temps suivant :

**Question 4**

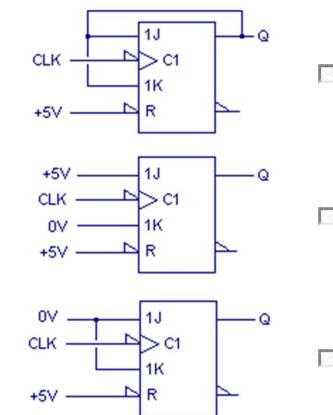

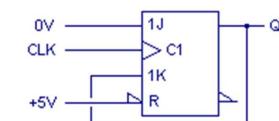

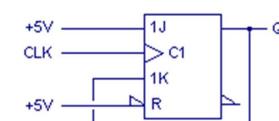

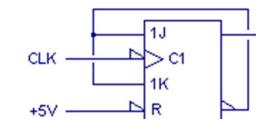

Indiquer le(s) montage(s) correspondant au diagramme des temps proposé.

**Question 5**

Indiquer le(s) montage(s) correspondant au diagramme des temps proposé.

**Question 6**

Indiquer le(s) montage(s) correspondant au diagramme des temps proposé.

**Question 7**

Indiquer le montage correspondant au diagramme des temps proposé.

Chapitre 7 :

# Machines à états

```

graph LR

b((b)) -- "b;0;R" --> c((c))

b -- "b;1;R" --> f((f))

c -- "b;1;R" --> e((e))

f -- "b;1;R" --> e

```

IUT GEII - Grenoble

## I. Introduction :

- Composées d'états et de transitions, les machines à états permettent de décrire des systèmes séquentiels

- Les états sont représentés par des cercles

- Les transitions sont représentées par des flèches

- FSM = finite state machine

2

## I. Introduction :

Deux types de machines à états:

- les machines de MEALY associent les actions (ou sorties) aux transitions

- les machines de MOORE associent les actions (ou sorties) aux états

**Nous aborderons uniquement les machines de Moore**

3

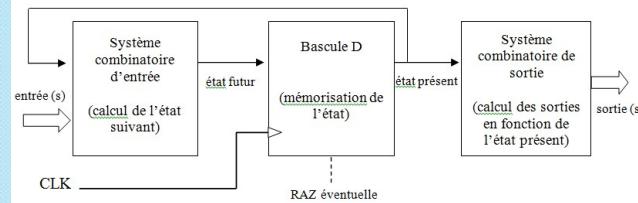

## II. Machines de MOORE :

- les valeurs des variables de sortie dépendent uniquement de l'état présent

- dans ce cas, le changement des sorties est **synchrone** : il se fait avec le changement des états

4

## II. Machines de MOORE :

Structure :

5

## II. Machines de MOORE :

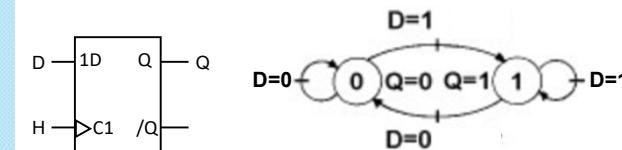

- Exemple d'une bascule D active sur front montant

Graphe synchronisé sur les fronts montants de H et avec 2 états qui correspondent ici aux valeurs de la sortie Q (Etat 0  $\equiv$  Q=0)

6

## II. Machines de MOORE :

### Exemple d'illustration :

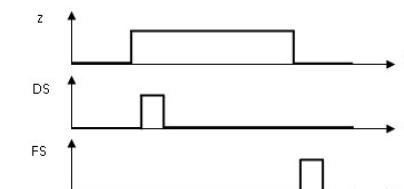

On souhaite détecter le début (DS) et la fin (FS) d'un signal  $z$  asynchrone par rapport à l'horloge CLOCK du système (**durée de  $z > 1$  période de l'horloge**).

Le système étudié devra générer une impulsion DS au début du signal  $z$  et une impulsion FS à la fin du signal  $z$ .

7

## II. Machines de MOORE :

### Exemple d'illustration :

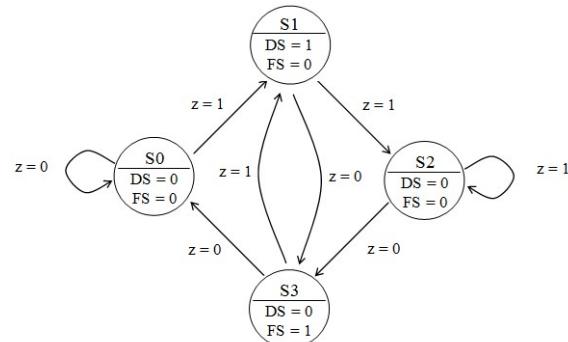

Nous avons donc :

- une entrée ( $z$ )

- et deux sorties (DS et FS)

8

## II. Machines de MOORE :

Graphe de transition (de l'exemple) :

9

## II. Machines de MOORE :

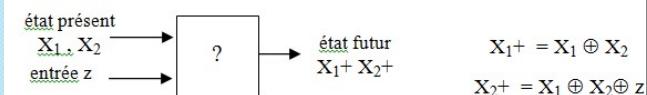

Codage du graphe :

- Pour coder 4 états, on utilise deux variables intermédiaires  $X_1$  et  $X_2$  (donc deux bascules D)

| $X_1$ | $X_2$ | état |

|-------|-------|------|

| 0     | 0     | S0   |

| 0     | 1     | S1   |

| 1     | 0     | S2   |

| 1     | 1     | S3   |

$X_1X_2$  est l'état présent

$X_1+X_2+$  est l'état futur

10

## II. Machines de MOORE :

Table de vérité :

| $z$ | $X_1$ | $X_2$ | $X_1+$ | $X_2+$ | DS | FS |

|-----|-------|-------|--------|--------|----|----|

| 0   | 0     | 0     | 0      | 0      | 0  | 0  |

| 0   | 0     | 1     | 1      | 1      | 1  | 0  |

| 0   | 1     | 0     | 1      | 1      | 0  | 0  |

| 0   | 1     | 1     | 0      | 0      | 0  | 1  |

| 1   | 0     | 0     | 0      | 1      |    |    |

| 1   | 0     | 1     | 1      | 0      |    |    |

| 1   | 1     | 0     | 1      | 0      |    |    |

| 1   | 1     | 1     | 0      | 1      |    |    |

valeur des sorties dans l'état présent

11

## II. Machines de MOORE :

Système combinatoire d'entrée :

12

## II. Machines de MOORE :

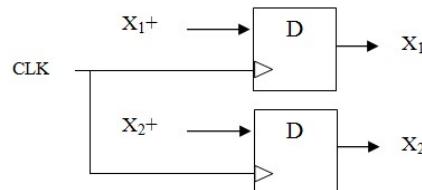

Bascules D :

13

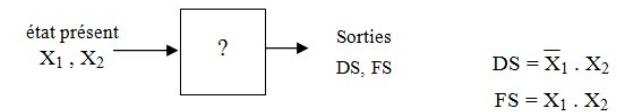

## II. Machines de MOORE :

Système combinatoire de sortie :

14

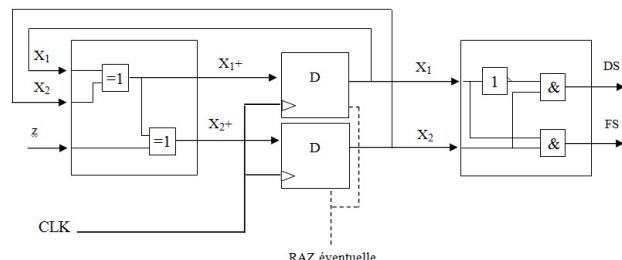

## II. Machines de MOORE :

Réalisation pratique :

15

## III. Conclusion :

- On utilise les machines de Moore car ses sorties sont synchronisées donc leur durée est toujours un multiple entier de la période du signal d'horloge

- Rem: en automatisme 2<sup>ème</sup> partie le grafset est une machine de Moore

16

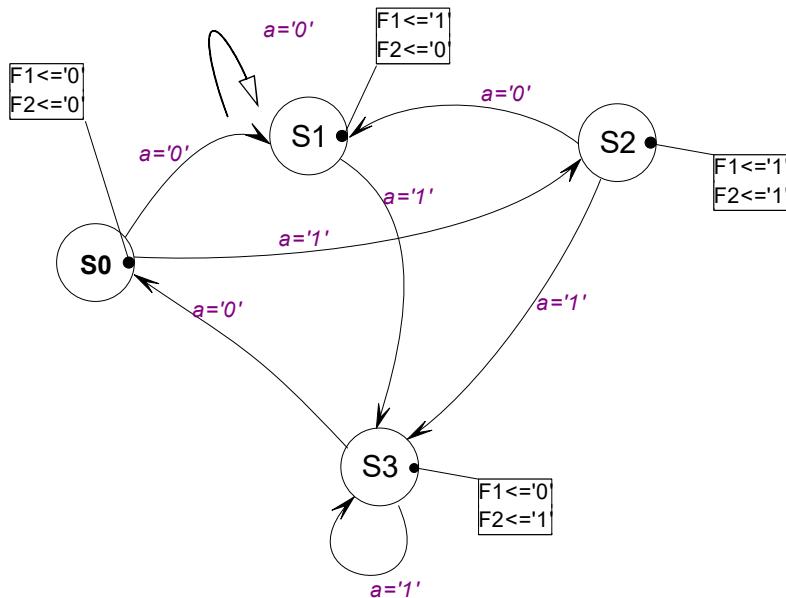

## TD Chap 7 MACHINES A ETATS

### Exercice 1

Un système séquentiel est décrit sous forme d'une machine à états de la façon suivante. (cf diagramme des états).

La variable  $a$  représente 1 capteur (actif à l'état H), les sorties sont appelées F1 et F2

### Réalisation matérielle avec des bascules

Pour réaliser cette machine de Moore, on code les 4 états à l'aide de 2 bascules dont les sorties Q0 et Q1 correspondent respectivement au N° de l'état (exemple : état S2 : Q1= 1 et Q0=0, état S3 : Q1= 1 et Q0= 1).

#### **1.1. Compléter la table de vérité suivante :**

Note : Q0+, et Q1+ sont les états futurs de Q0 et Q1.

| a | Q1 | Q0 | Q1+ | Q0+ | F1 | F2 |

|---|----|----|-----|-----|----|----|

| 0 | 0  | 0  |     |     |    |    |

| 0 | 0  | 1  |     |     |    |    |

| 0 | 1  | 0  |     |     |    |    |

| 0 | 1  | 1  |     |     |    |    |

| 1 | 0  | 0  |     |     |    |    |

| 1 | 0  | 1  |     |     |    |    |

| 1 | 1  | 0  |     |     |    |    |

| 1 | 1  | 1  |     |     |    |    |

1.2. En déduire les équations des fonctions Q0+, Q1+ et des sorties F2 et F1.

- Q0+ =

- Q1+ =

- F1 =

- F2 =

1.3. Représenter le schéma structurel de ce système séquentiel à partir de bascules D.

### Exercice 2 :

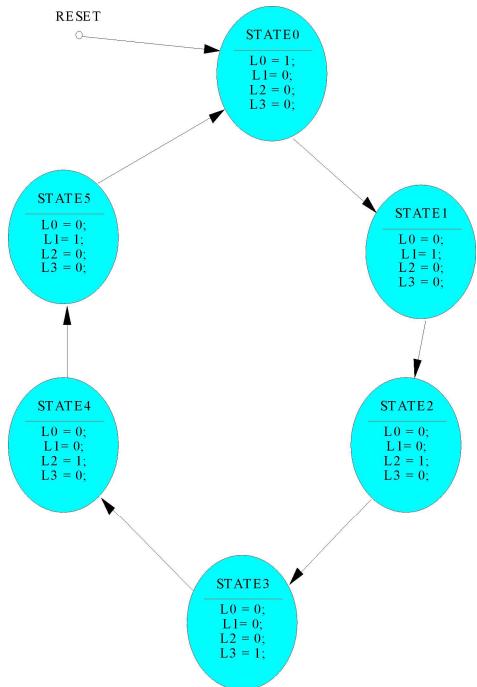

Il s'agit d'un système séquentiel qui comporte 4 LEDs (L3, L2, L1 et L0) qui vont s'allumer successivement de droite à gauche puis de gauche à droite. Il peut être décrit sous forme d'une machine à états de la façon suivante.

### Réalisation matérielle avec des bascules

Pour réaliser cette machine de Moore, on code les 6 états à l'aide de 3 bascules dont les sorties Q0, Q1 et Q2 correspondent respectivement au N° de l'état (exemple : STATE2 : Q2= 0, Q1= 1 et Q0=0, STATE5 : Q2=1, Q1= 0 et Q0= 1).

#### **1.4. Compléter la table de vérité suivante :**

Note : Qi+ est l'état futur de Qi.

| Q2 | Q1 | Q0 | Q2+ | Q1+ | Q0+ | L3 | L2 | L1 | L0 |

|----|----|----|-----|-----|-----|----|----|----|----|

| 0  | 0  | 0  |     |     |     |    |    |    |    |

| 0  | 0  | 1  |     |     |     |    |    |    |    |

| 0  | 1  | 0  |     |     |     |    |    |    |    |

| 0  | 1  | 1  |     |     |     |    |    |    |    |

| 1  | 0  | 0  |     |     |     |    |    |    |    |

| 1  | 0  | 1  |     |     |     |    |    |    |    |

#### **1.5. En déduire les équations des fonctions Q2+, Q1+ Q0+**

- Q0+ =

- Q1+ =

- Q2+ =

#### **Puis des sorties**

- L3 =

- L2 =

- L1 =

- L0 =

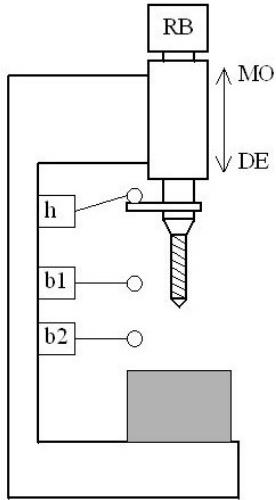

### **Exercice 3 : Commande d'une perceuse, une première approche du GRAFCET**

Soit une perceuse à colonne qui possède un moteur de rotation de la broche RB, une commande de descente rapide DE GV (comme Grande Vitesse), une commande de descente lente DE PV (comme Petite Vitesse), une commande de montée MO. Le départ cycle sera assuré par un bouton poussoir dcy actif H, 3 contacts fin de course h, b1, et b2 permettent de connaître la position de la perceuse. Tous les contacts de fin de course sont normalement ouvert donc actif H.

#### **Fonctionnement :**

Au repos la perceuse est en haut.

L'opérateur lance un cycle par l'appui sur dcy. La broche est actionnée, une descente rapide est activée jusqu'à la position b1, puis la descente se fait lentement jusqu'à la position b2 (fin du perçage).. La perceuse remonte jusqu'à sa position initiale et la broche s'arrête de tourner.

1. Lister dans un tableau les entrées et les sorties

2. Représenter sous forme de machine à état le fonctionnement. A la mise sous tension le système sera dans un état (ou étape) initial S0.

*Note : Pour réaliser cette machine de Moore, on codera les à l'aide de bascules dont les sorties Q0, Q1 correspondent respectivement au N° de l'état*

3. Donner les équations de commande des bascules  $Q0^+$  et  $Q1^+$

4. Donner les équations des sorties en fonction des états présents (combinatoire de fin de cycle)

• Chapitre 8 :

## Registres et compteurs

IUT GEII - Grenoble

### Plan du chapitre :

1. Généralités

2. Fonction comptage

3. Compteurs asynchrones

4. Compteurs synchrones

5. Utilisation des compteurs synchrones

6. Registres de mémorisation

2

### 1. Généralités:

On rencontre trois types de registres synchronisés sur front d'horloge qui assurent les fonctions suivantes :

- **la fonction mémorisation** : une information placée à l'entrée est copiée dans le registre.

- **la fonction comptage** : à partir d'une valeur N caractérisant le contenu du registre, celui-ci passe ensuite la valeur N+1.

- **la fonction décalage** : l'état des bascules qui constituent le registre se décale d'un rang.

3

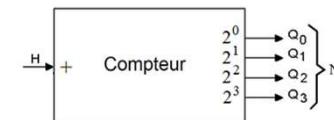

### 2. Fonction comptage

- **Compteur** : Structure permettant de dénombrer les événements (H) qui lui sont appliqués

Registre particulier dont le contenu évolue, passe de la valeur N à la valeur N+1, après une impulsion de progression

- **Elément de base des compteurs** : bascules JK ou D synchronisées sur front

- **Etat du compteur** : nombre binaire N formé des sorties pondérées ( $Q_0, Q_1, \dots, Q_n$ )

4

## 2. Fonction comptage

- Le code peut être du **binaire pur** (compteur binaire) ou un autre code comme **BCD** :

- Compteur binaire pur où avec n bits:

$N = Q_{n-1} \cdot 2^{n-1} + \dots + Q_5 \cdot 2^5 + Q_4 \cdot 2^4 + Q_3 \cdot 2^3 + Q_2 \cdot 2^2 + Q_1 \cdot 2^1 + Q_0 \cdot 2^0$

- Compteur BCD où avec n=8 bits:

$N = (Q_7 \cdot 2^7 + \dots + Q_4 \cdot 2^4) \cdot 10^1 + (Q_3 \cdot 2^3 + Q_2 \cdot 2^2 + Q_1 \cdot 2^1 + Q_0 \cdot 2^0) \cdot 10^0$

- Rôle des compteurs (ou décompteurs) ou « timers » :** Temporisateur (génération d'une temporisation), compteur d'événements et/ou diviseur ou prédiviseur de fréquence

Classés en 2 catégories : **compteurs asynchrones ou synchrones**

5

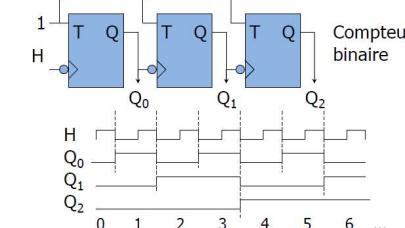

## 3. Compteurs Asynchrones

Un compteur Asynchrone de n bits est constitué de n diviseurs par 2 (bascules T) MIS EN CASCADE

On distingue 2 types de compteurs asynchrones:

- Compteur proprement dit

Cascade de diviseurs de fréquence sur fronts descendants

6

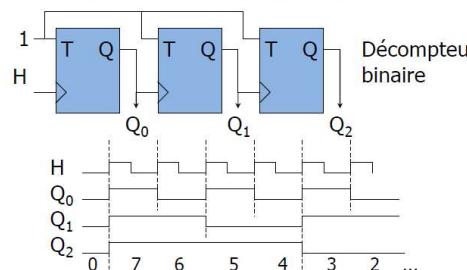

## 3. Compteurs Asynchrones

- Décompteur

Cascade de diviseurs de fréquence par deux sur fronts montants

7

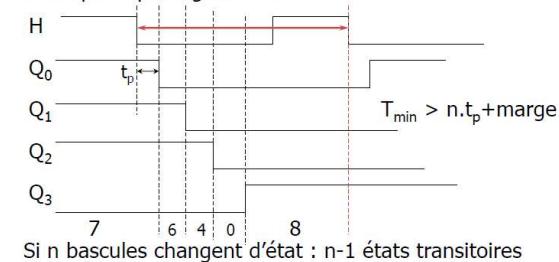

## 3. Compteurs Asynchrones

- Problème

Accumulation des temps de propagation

Exemple : passage de 7 à 8

8

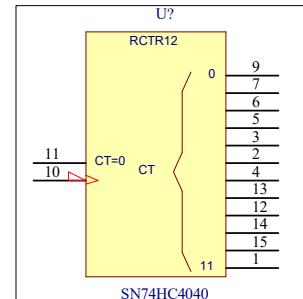

### 3. Compteurs Asynchrones

Exemple: compteur 12 bits (sorties de  $Q_0$  à  $Q_{11}$ ) avec Reset Asynchrone et horloge active sur front descendant.

9

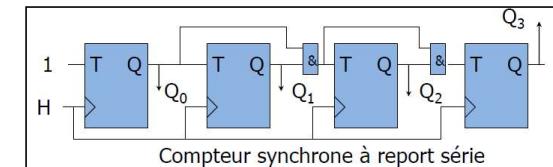

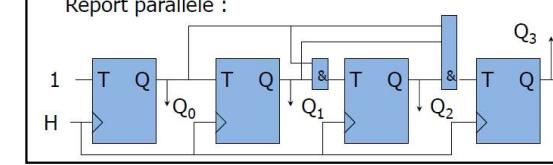

### 4. Compteurs Synchrones

Un compteur synchrone possède une horloge COMMUNE à toutes les bascules T

Report parallèle :

Compteurs 4 bits un exemple

10

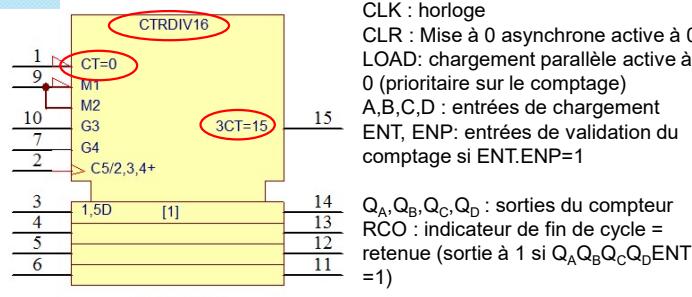

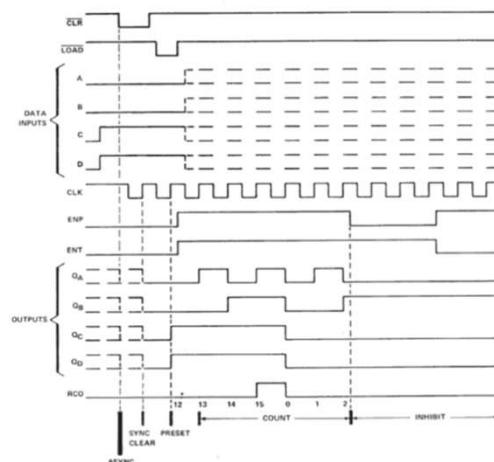

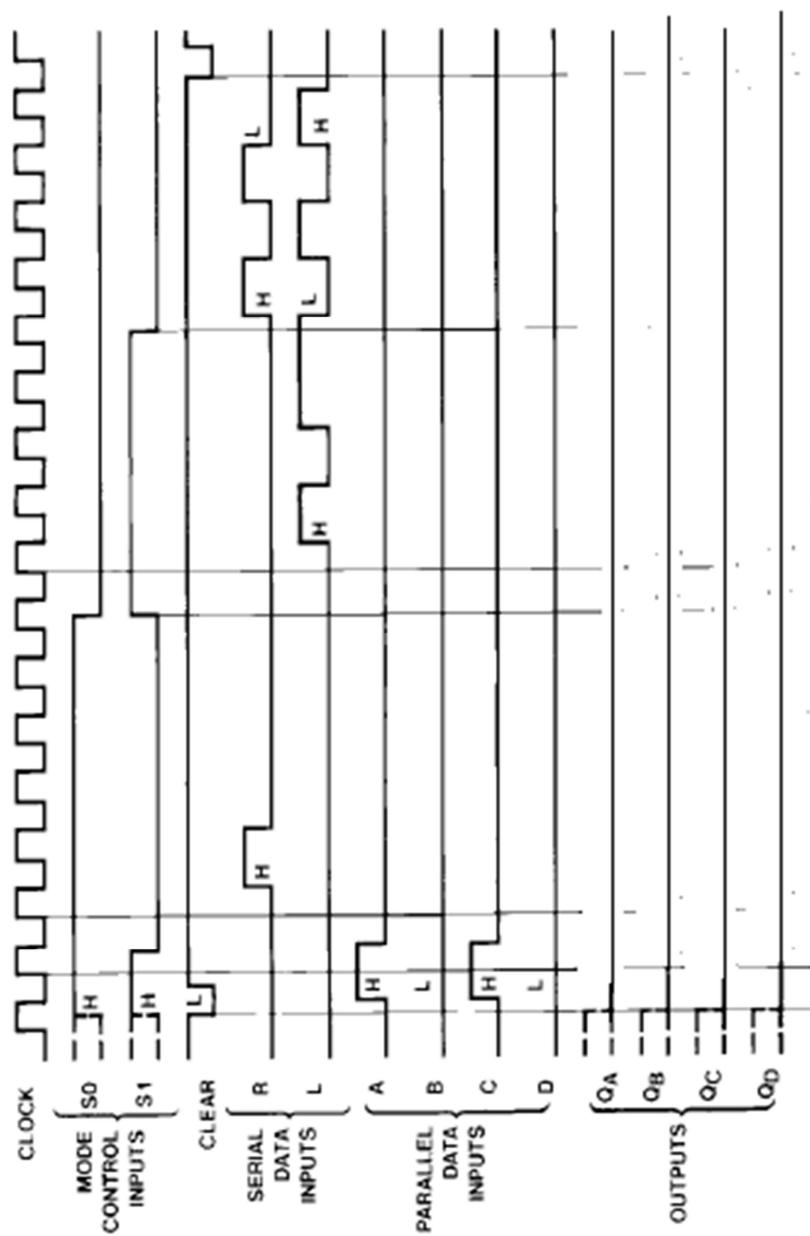

### 4. Compteurs Synchrones

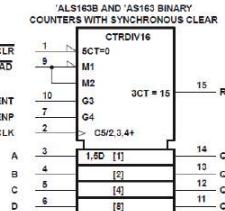

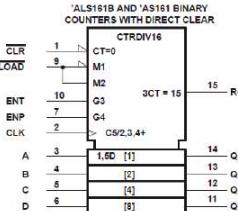

74161 : Compteur synchrone (sur front montant) binaire 4 bits (avec RAZ asynchrone et chargement parallèle synchrone)

SN74HC161

11

### 4. Compteurs Synchrones

Exemple: chronogramme du 74xx161:

12

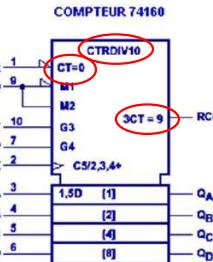

## 4. Compteurs Synchrones

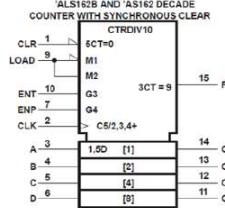

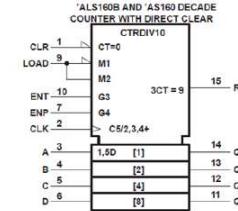

74160 compteur intégré synchrone 4 bits BCD (RAZ asynchrone) programmable cascadable de la famille TTL (16 broches (pins))

|                            | INPUTS |     |     |     |      |    | OUTPUTS |     |

|----------------------------|--------|-----|-----|-----|------|----|---------|-----|

| Operating mode             | CLR    | CLR | ENP | ENT | LOAD | Pn | Qn      | RCO |

| Reset (clear) asynchronous | L      | X   | X   | X   | X    | X  | L       | L   |

| Parallel load              | H      | ↑   | X   | X   | L    | L  | H       | H   |

| count                      | H      | ↑   | H   | H   | H    | X  | count   |     |

| Hold (do nothing)          | H      | X   | L   | X   | H    | X  | qn      | L   |

|                            | H      | X   | X   | L   | H    | X  | qn      | L   |

Note : 74162 = compteur BCD 4 bits (RAZ synchrone)

13

## 4. Compteurs Synchrones

### Synthèse

14

## 4. Compteurs Synchrones

### Caractéristiques temporelles

Paramètres à respecter : entrée statique par rapport à une horloge

L'entrée statique doit être stable pendant  $t_{SU}$  avant et  $t_h$  après l'horloge.

Si ces conditions ne sont pas respectées, il y a risque (statistique) de métastabilité; niveau non garanti, temps de propagation très long ...

15

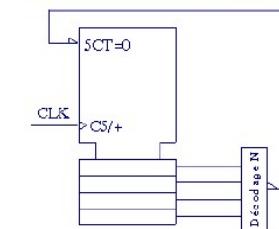

## 5. Utilisation des compteurs synchrones

### Compteur à cycle incomplet de 0 à $N < 2^n$

nécessite le décodage de la valeur maximale N à atteindre afin d'activer de la remise à 0 si elle est synchrone

16

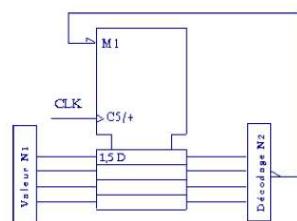

## 5. Utilisation des compteurs synchrones

### Compteur à cycle incomplet de N1 à N2<2<sup>n</sup>

nécessite le décodage de la valeur maximale N2 à atteindre afin de faire un chargement parallèle synchrone de la valeur N1

17

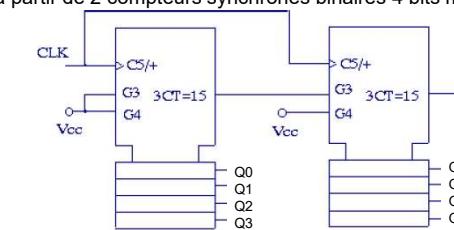

## 5. Utilisation des compteurs synchrones

### Mise en cascade de compteurs:

- Utilisation des compteurs synchrones 4 ou 8 bits proposés par les constructeurs pour réaliser des compteurs synchrones de plus grande taille.

- Utilisation de la sortie de retenue (RCO) pour activer le comptage du compteur mis en cascade suivant

- Exemple :** réalisation d'un compteur synchrone binaire 8 bits (Q0, Q1, ..., Q7) à partir de 2 compteurs synchrones binaires 4 bits mis en cascade

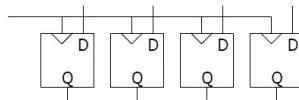

## 6. Registres de mémorisation

Un registre est un ensemble de bascules D possédant la même horloge (CLK)

Exemple

Applications

- registre d'interface entre des sous-ensembles : l'information traitée par un sous-ensemble est mémorisée dans un registre pour être ultérieurement utilisée par un autre sous-ensemble.

- registre de stabilisation d'états instables

19

**TD Chap 8 Systèmes séquentiels : compteurs**

Ressources : cours chapitre 8 et documents constructeurs

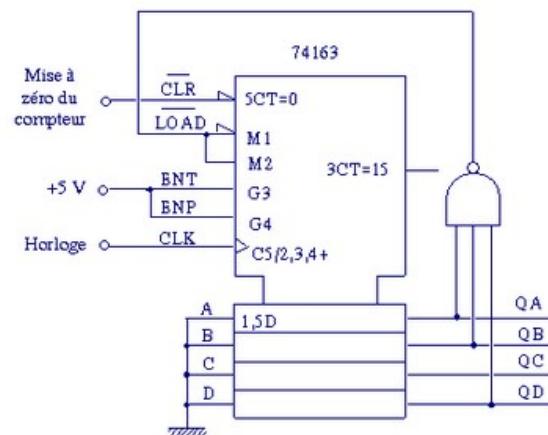

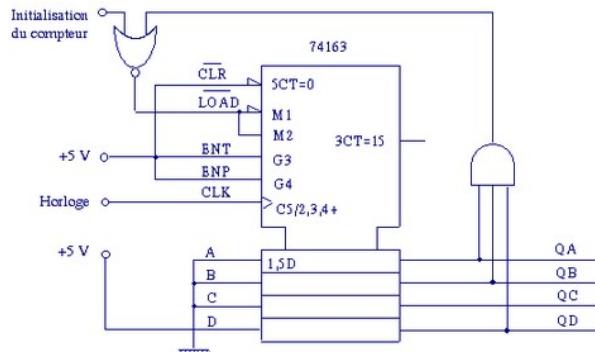

Exercice 1 : Analyse de schémas réalisés avec un compteur 74163

Déterminer le **cycle de fonctionnement** des montages suivants :

## 1. montage 1

## 2. montage 2

## **Exercice 2 : Réalisation de schémas (à partir d'un compteur 74163)**

1. Proposer un schéma permettant de réaliser un **compteur modulo 8**. (voir montage 1)

2. En vous inspirant du montage 2 proposer une réalisation (schéma structurel) d'un compteur présentant le **cycle de fonctionnement suivant : 4, 5, 6, 7**. Ces chiffres correspondent à la représentation décimale de l'état des sorties.

### **Exercice 3 : Association de compteurs**

1. Réaliser un schéma correspondant à un **compteur binaire modulo 30 à progression synchrone**.

2. Proposer un schéma d'un **compteur BCD modulo 24**.

#### **Exercice 4 : Génération d'une temporisation.**

On désire réaliser une température de **12,8 ms** à partir d'une horloge de **1 MHz**.

Dans un premier temps on va **prédiviser** cette fréquence à l'aide d'un compteur 8 bits.

On utilisera ensuite un **deuxième compteur** pour faire la temporisation. La durée de la temporisation sera donnée entre le moment du chargement parallèle d'une valeur initiale et la levée du drapeau RCO qui correspond à l'overflow c'est-à-dire lorsque la valeur du compteur passe de **255 à 0**.

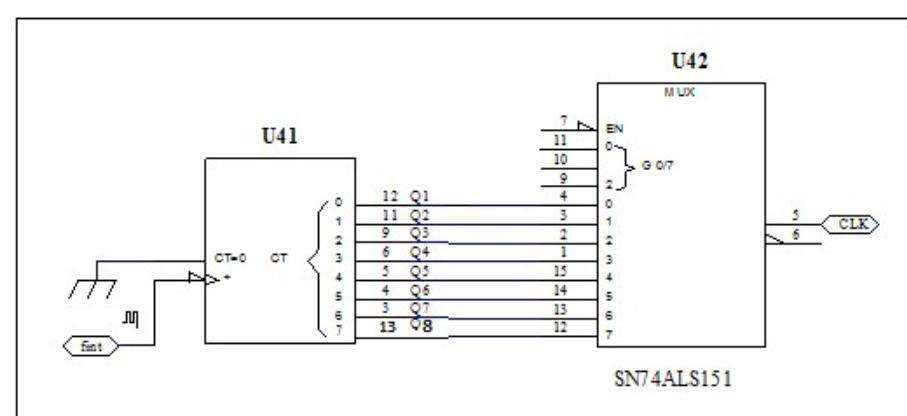

## 1. Etude du prédiviseur :

L'horloge CLK est donc fournie par la sortie d'un **multiplexeur** qui sélectionne une des 8 sorties du prédiviseur. On utilisera un compteur 8 bits.

On veut une horloge CLK de fréquence  $f_{\text{clk}} = 15.625 \text{ kHz}$

- a. Quelle sortie faudra-t-il sélectionner ?

- b. Compléter le schéma précédent pour avoir  $f_{clk} = 15,625 \text{ kHz}$ .

- c. En déduire la période  $T_{clk}$ .

2. Etude du compteur.

- a. Combien d'impulsion  $T_{clk}$  faut-il compter pour obtenir **une durée de 12,8 ms** ?

- b. En déduire **la valeur initiale de chargement en décimal** puis en binaire pour obtenir cette temporisation.

## Chapitre 9 : Registres à décalage (shift registers)

### Plan du chapitre

- I. Définition

- II. Principaux types

- III. Exemple

- IV. Utilisation

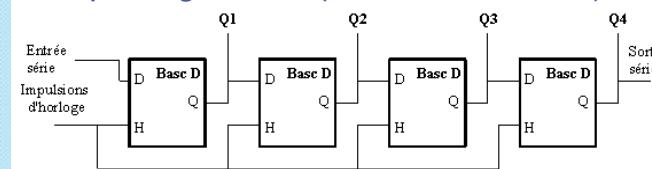

#### I. Définition

Le principe de réalisation d'un registre à décalage consiste simplement à relier la sortie de chaque bascule sur l'entrée de donnée de la bascule suivante, toutes les bascules étant synchronisées par la même horloge .

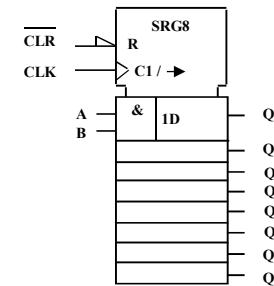

##### Exemple de registre 4 bits : (Entrée série – Sortie série)

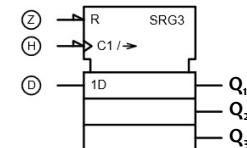

- La représentation symbolique la plus simple d'un registre à décalage est donnée ci-dessous :

avec

**SRG** : shift register (symbole du registre à décalage). Le chiffre qui suit ce symbole est celui des cellules constituant le registre (3 en l'occurrence).

**Z** : reset

**H** : commande de chargement et décalage (active sur un front ici descendant). Elle est affectée du symbole de décalage (→).

**D** : entrée de donnée (dans ce cas en série)

**Qi** : sorties

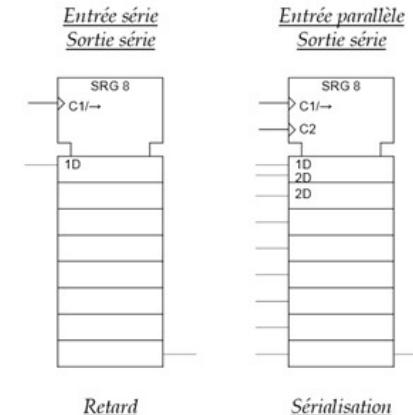

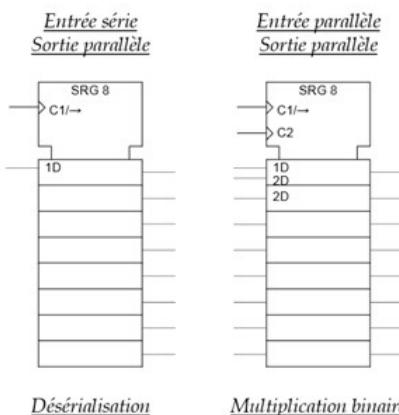

## II. Principaux types

- De nombreuses fonctions peuvent être ajoutées à la structure élémentaire d'un registre à décalage. En particulier, certains registres à décalage permettent d'effectuer un **chargement de données en parallèle et/ou série**.

- Ainsi, il existe quatre types de registre selon le mode d'accès au registre (en lecture et en écriture)

- > Registre à mode d'écriture série et mode de lecture série.

> Registre à mode d'écriture parallèle et mode de lecture série.

- > Registre à mode d'écriture série et mode de lecture parallèle.

> Registre à mode d'écriture parallèle et mode de lecture parallèle.

## III. Exemple

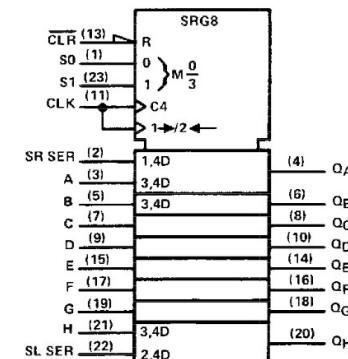

- Un des registres à décalage le plus complet disponible en circuit intégré est le 74198 dont la représentation symbolique est la suivante :

## TD Chapitre 9 : REGISTRES A DECALAGE

### Exercice 1 :

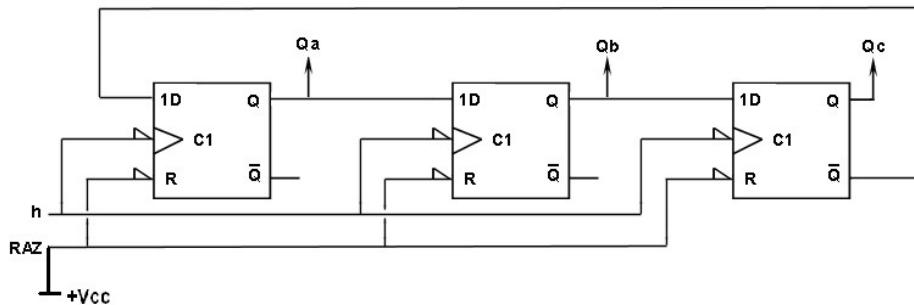

Soit le schéma suivant :

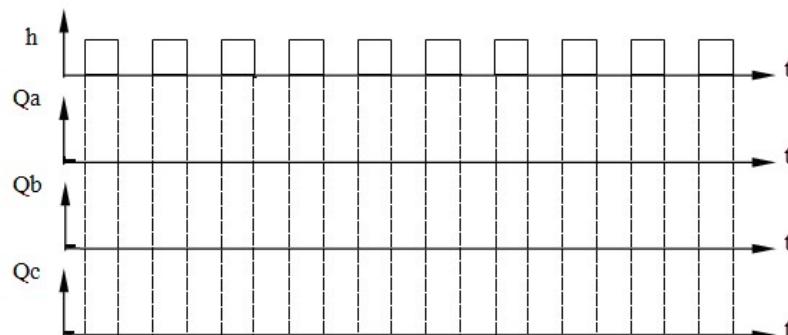

1. Compléter les chronogrammes (en considérant  $Q_a = Q_b = Q_c = 0$  à l'instant initial)

2. Quelle est la particularité du code engendré par les sorties  $Q_a$ ,  $Q_b$ ,  $Q_c$  des bascules ?

3. On désire remplacer la structure précédente (3 bascules D) par un SN74LS164 dont le symbole normalisé est donné page suivante.

- a. Quelle est la fonction de ce composant ?

- b. Compléter le schéma en rajoutant un seul circuit élémentaire de façon à réaliser le même fonctionnement

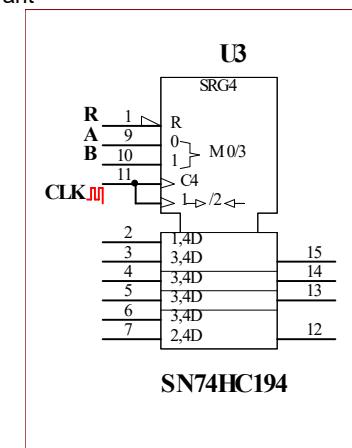

### Exercice 2 :

Soit le circuit U3 suivant

1. Compléter la table de fonctionnement (indiquer la fonction réalisée) :

| B | A | R | CLK | Fonction Réalisée |

|---|---|---|-----|-------------------|

| X | X | L | X   |                   |

| L | L | H | ↑   |                   |

| L | H | H | ↑   |                   |

| H | L | H | ↑   |                   |

| H | H | H | ↑   |                   |

2. Compléter le chronogramme suivant

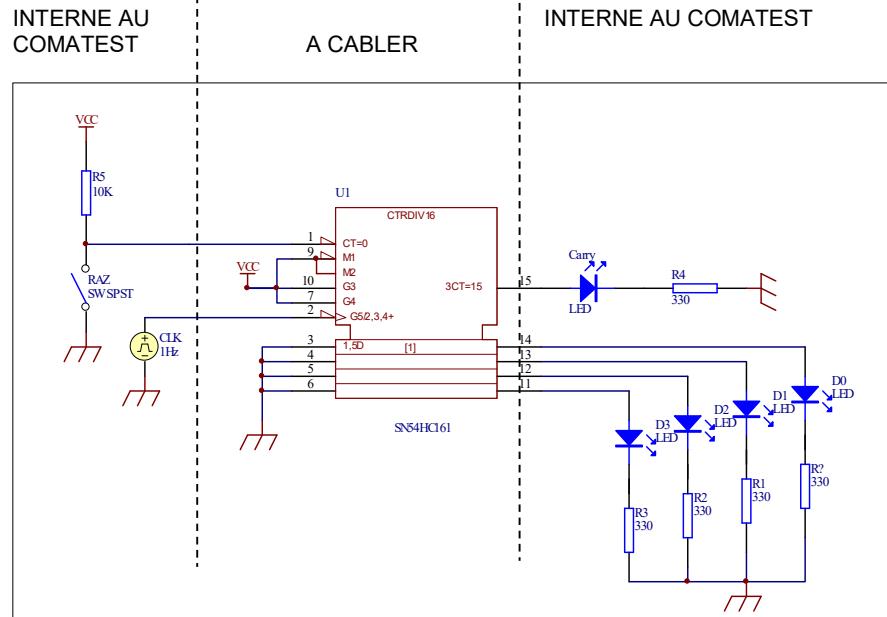

## TP SIN 2

### **Matériels :**

- platine « Comatest »,

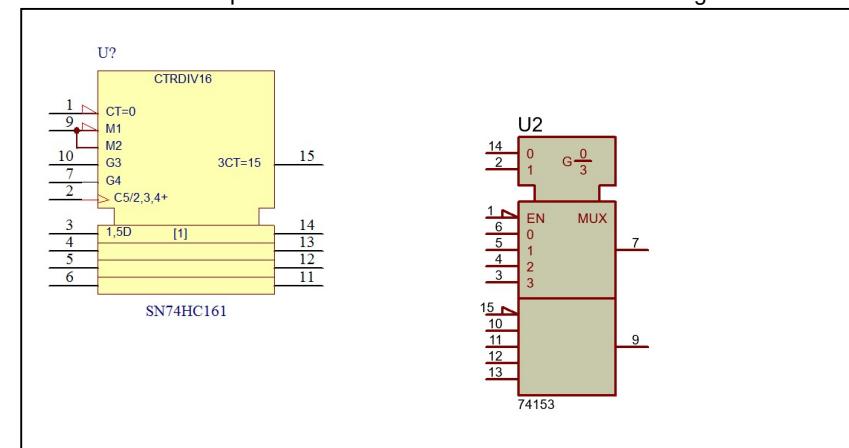

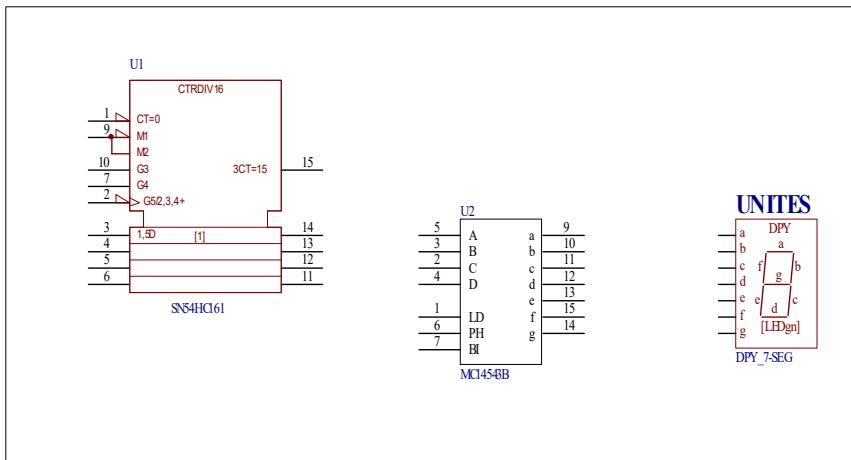

- Compteurs synchrones binaires 74HC161

- Multiplexeur 4 vers 1 : 74LS153

- Décodeur BCD / 7 segments 4543

- Portes élémentaires et composants passifs

- Afficheur 7 segments à cathodes communes MAN74A

La présence du symbole ► indique que vous devez faire valider ce point par un enseignant. Un compte-rendu par binôme avec schémas propres et repérés sera à fournir en fin de séance.

## 1. Compteur à cycle complet

a) Câbler le montage suivant :

On prendra l'horloge de 1 Hz disponible sur le comatest que vous connecterez également sur une LED rouge et un bouton poussoir de RAZ. Les 4 sorties du compteur doivent être, dans un premier temps, connectées directement sur 4 LEDs rouges de la platine dont on indiquera le numéro des broches. Le poids

fort sera une LED à gauche et le poids faible une LED à droite. La sortie de retenue sera également connectée.

- Vérifier le fonctionnement sur un cycle complet (progression, retenue et remise à zéro)

Quelle est la période des sorties D0 et D3 du compteur ?

**NE PAS DECABLER**

- b) Proposer une réalisation (schéma structurel et câblage) qui utilise un multiplexeur 4 vers 1 afin de sélectionner une des 4 sorties du compteur grâce à 2 entrées de sélection que vous connecterez sur 2 interrupteurs du comatest. La sortie du multiplexeur devra être connectée sur une LED rouge.

- Vérifier le fonctionnement de votre réalisation.

Quelles valeurs des entrées de sélection permettent d'avoir en sortie du multiplexeur un signal de fréquence 0.125 Hz ?

***NE PAS DECABLER le compteur, DECABLER le multiplexeur***

- c) Compléter le schéma de câblage du compteur à cycle complet (question a) afin de visualiser les nombres sur un afficheur 7 segments à cathodes communes. On utilisera un décodeur BCD/7 segments.

#### **Conseil :**

- ☞ Utiliser la documentation du constructeur pour le brochage

- ☞ Vérifier que l'afficheur 7 segments est bien à cathodes communes.

- Vérifier le fonctionnement sur un cycle complet. Que constatez-vous ? Conclusion.

#### **NE PAS DECABLER**

#### **2. Compteur modulo 5**

Proposer une réalisation (schéma structurel et câblage) d'un compteur présentant **le cycle de fonctionnement suivant : 4, 5, 6, 7, 8**. Ces chiffres correspondent à la représentation décimale de l'état des sorties. Prévoir une entrée d'initialisation dont un repèrera le N° du BP du comatest.

- Vérifier le fonctionnement sur un cycle complet.

#### **3. Mise en cascade de compteurs**

Proposer une réalisation (schéma structurel et câblage) d'un compteur binaire présentant **le cycle de fonctionnement variant de 49 à 65**. Prévoir une entrée d'initialisation dont on repèrera le N° du BP du comatest permettant de charger la **valeur 49**.

- Vérifier le fonctionnement sur un cycle complet.